3 가지로 차별화 된 모바일 시장

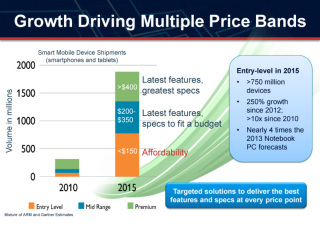

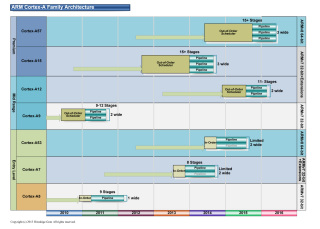

스마트폰과 태블릿 시장은 세 가지로 분화하고 있다. 하이 엔드 및 미드 레인지, 그리고 엔트리 레벨 3 계층이다. ARM은 이러한 계층 분화에 따라 CPU 코어와 GPU 코어도 계층화하고 있다. 예를 들어, 기존에는 2 계층이었다 CPU 제품군의 구성을 다른 전력과 성능 및 비용 "PPA (Power, Performance and Area)"균형 3 계층으로 심화시키고 있다. 현재 라인업으로 말하면 Cortex-A15가 프리미엄, Cortex-A9가 미드 레인지, Cortex-A7 (조금 전은 Cortex-A8 싱글 코어)가 엔트리 레벨이 된다.

이러한 3 개의 계층은 장치의 가격 범위가 다르다. 프리미엄은 400 달러 전후에서의 가격대 시장, 중급은 200 ~ 350 달러 전후까지의 가격대의 시장, 그리고 엔트리 레벨은 150 달러 전후에서 아래의 시장이다. 그리고 현재 성장하고 있는 아래 두 계층이라고 한다.

무엇보다,이 가격대의 이야기는 "응?"라고 느끼는 사람도 많을지도 모른다. 일본이나 미국 등 많은 나라에서 2년 약정에 의한 할부 판매에서 프리미엄 가격대의 스마트폰도 낮은 초기 비용으로 구입이 가능하기 때문이다. 따라서 프리미엄 세그먼트의 제품이 지배적이다. 그러나 ARM이 보여주고 있는 것은 어디 까지나 단말기 자체의 가격 라인이다. 그리고 할부 판매를 취하기 어려운 국가 나 지역에서는 이를 위해 가격이 중요한 의미를 갖는다. 그러한 국가 나 지역에서는 스마트폰과 태블릿이 보급에 따라 저렴한 가격의 미드 레인지 및 엔트리 레벨이 성장 경향이 강해지고 있다.

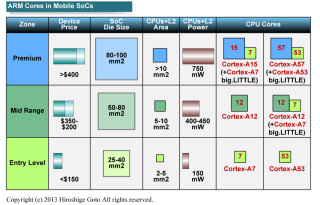

장치의 가격대가 다르다면 제조 비용에 따라 칩도 다르다. 구체적으로는 각 가격 범위에서 장치에 탑재되는 모바일 SoC의 다이 크기가 다르다. ARM에 따르면 프리미엄 장치의 SoC는 80 ~ 100 평방 mm 정도 또는 그 이상의 미드 레인지 SoC는 50 ~ 80 평방 mm, 엔트리 레벨의 SoC는 25 ~ 40 평방 mm가 된다.

등급에 따른 CPU 코어 크기

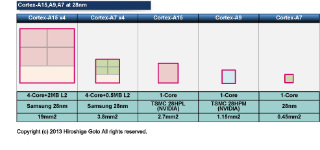

SoC의 다이 크기가 다르면 SoC에 싣는 수있는 CPU 코어 부분의 다이 면적도 달라진다. ARM은 멀티 프로세서 구성의 CPU 코어와 L2 캐시의 총 면적에서 중급이라면 5 ~ 10 평방 mm가 적절하다고 추정하고 있다. 이것이 프리미엄이 되면 10 평방 mm 대에서 20 평방 mm에 가까운 범위까지 허용된다. 하지만 엔트리 레벨이 되면 CPU의 면적은 2 ~ 5 평방 mm로 억제된다. 일반적으로는 엔트리 레벨 → 중급 → 고급에서 CPU 코어 + L2의 크기는 배로 늘어난다. SoC 다이 전체의 수십 %를 CPU로 사용하는 셈이다.

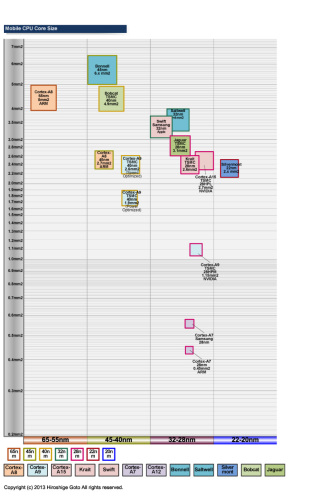

CPU에 할애 할 수있는 다이 면적이 한정되면 CPU 코어의 크기도 결정된다. 쿼드 코어 구성이라면 프리미엄의 CPU 코어 면적은 2 ~ 3 평방 mm 대의 미드 레인지는 1 ~ 1.5 평방 mm 정도, 엔트리 레벨은 0.5 평방 mm 전후가 될 것으로 추측된다. 아래의 CPU 코어 구현의 예를 보면 그 추측의 범위에 들어 갔는지 알 수 있다.

다이 면적과 함께 CPU 부분의 소비 전력도 제한된다. 멀티 코어 CPU 플러스 L2 캐시의 전력 소비의 기준은 프리미엄에서 750mW, 중급 400 ~ 450mW 엔트리 레벨에서 150mW 범위라고 한다.

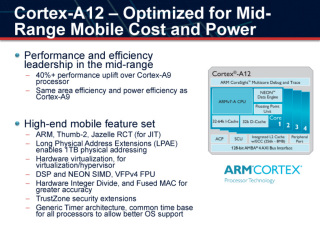

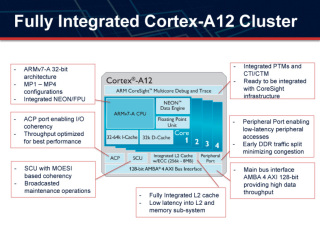

CPU 면적과 전력이 결정되면 CPU 코어 종류가 필연적으로 정해진다. 내년 (2014 년)의 라인업이라면 프리미엄이 Cortex-A15 또는 Cortex-A15와 A7의 big.LITTLE 구성 엔트리 레벨이 Cortex-A7의 듀얼 또는 쿼드 구성, 그리고 미드 레인지를 담당하는 것이 새로운 "Cortex-A12 '이다. 이것은 64 bit 화가 진행 시작하면 프리미엄이 Cortex-A57와 A53 엔트리 레벨도 Cortex-A53가 부분적으로 침투한다. 하지만 미드 레인지는 그 단계에서 Cortex-A12가한다.

Cortex-A9 이후 경험치를 높인 ARM

Cortex-A9는 스마트폰과 태블릿의 대표적인 CPU 코어로 지난 3 년간 시장을 석권 해왔다. ARM의 Stephane Brochier 씨 (Consultant Engineer, Processors Division, ARM)에 따르면 "올해 (2013 년) 말까지 Cortex-A9의 출하 유닛 수는 10 억에 도달 핵심 IP 라이센스의 수는 60 개에 달한다" 한다. 사용되는 분야도 모바일뿐만 아니라 네트워크 장비, 서버, 디지털 TV와 홈 게이트웨이 등의 가전, 산업, 자동차 등 다방면에 걸친다. 한마디로 성공한 핵심이다.

ARM은 Cortex-A9의 성공의 원인을 2008 년 반도체 제조 업체에 제공을 시작한 코어로서는 선진적인 디자인이었다 때문이라고 분석한다. 모바일 용 CPU 코어의 대부분이 인 오더 실행 (Cortex-A8 등) 일 때 부분적이기는 하지만 듀얼 이슈의 아웃 오브 오더 실행을 채용. 4 코어까지 멀티 코어도 지원하고 당시의 모바일 CPU로 뛰어난 성능을 달성하면서 전력과 다이 면적도 억제했다.

그러나 2008 년에 출시 한 Cortex-A9는 5 년이 지난 지금은 결코 최신 모바일 CPU 아키텍처가 아니라 현재의 모바일 시장 상황에 적응하고 있다고는 말하기 어렵다. 따라서 ARM은 Cortex-A9와 같은 수준에서 아키텍처를 쇄신 한 CPU 코어를 개발하기로 했다. 그것이 Cortex-A12이다. ARM의 James Bruce 씨 (Lead Mobile Strategist, ARM)는 COMPUTEX시 다음과 같이 말하고 있다.

"Cortex-A9는 디자인을 시작했던 것이 2006 년이었다. 당시 당사의 엔지니어링은 아직 충분한 경험을 바탕되지 않았다고 말할 수 있을지도 모른다. 그러나 Cortex-A9 실제로 코드를 실행시켜 많은 분석 결과를 얻고 개선해야 할 점을 찾아 그 중 일부를 Cortex-A9r4에 담았다. 메모리 서브 시스템을 개선하는 등의 튜닝이다. Cortex-A12는 그러한 Cortex-A9 경험 을 거쳐 완전히 새로운 설계했다. "

Cortex-A9는 ARM에 최초의 아웃 오브 오더 실행 코어에서 다양한면에서 완벽했었다. Cortex-A12는 Cortex-A9와 동급 미드 레인지 디바이스 용 CPU 코어이다. 하지만 디자인은 완전히 일신되어 Cortex-A9에 대해 성능을 40 % 이상 향상시켰다. "동일한 전력 범위 내에서 대부분의 모바일 워크로드에서 Cortex-A9에 대해 40 % 또는 그 이상의 성능 향상을 달성했다. 성능 향상에 기여하고 있는 것은 주로 IPC (Instruction- per-Clock)의 향상이다. 동작 주파수는 Cortex-A9와 거의 다르지 않다 "고 ARM의 Brochier 고 말했다. Cortex-A9의 5 년 오래된 디자인을, 프롬 스크래치로 설계 다시하면 40 % 성능을 향상 여지가 있었다는 것이다.

32-bit의 미드 레인지 코어에 뚫린 구멍을 채우기

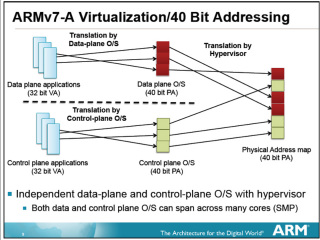

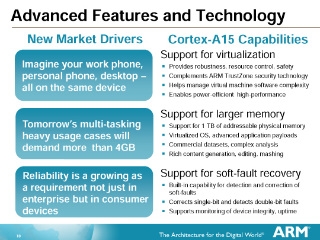

실제로 ARM의 CPU 코어 설계는 Cortex-A15에서 크게 바뀌었다. 보다 고성능 지향의 본격적인 아웃 오브 오더 실행 CPU 마이크로 아키텍처로 었다. 말하자면, Cortex-A9는 성능이 높은 CPU 코어를 위한 습작에서 Cortex-A15에서 그 경험을 살려 진 마이크로 아키텍처로 진화 한 분위기였다. ARM의 CPU 코어는 Cortex-A9와 A15에서의 도약이 세대가 나뉜다. 따라서 ARM은 중급 CPU에서 Cortex-A15 이상과 같은 세대 마이크로 아키텍처의 CPU를 필요로하고 있었다. 또한 명령어 세트면에서도 Cortex-A15와 동일 세대의 미드 레인지 코어가 부족했다.

Cortex-A9 및 후속 Cortex-A15/A7 같은 ARMv7 명령어 세트 아키텍처 기반이지만, Cortex-A15/A7에서는 명령과 기능이 확장되고 있다. 새로운 1TB까지 실제 메모리 주소 "Long Physical Address Extensions (LPAE)"고 하드웨어 가상화 지원이 더 해졌다. 또한 정수 나눗셈 등의 새로운 명령도 추가되었다. 그 때문에, 같은 ARMv7에도 Cortex-A9 및 Cortex-A15에서 부분적으로 호환이 되지 않는 부분이 발생했다.

ARM의 CPU 코어 IP의 라인업을 보면 이러한 사정을 잘 알 수 있다. ARM은 프리미엄과 보급형에서는 명령어 세트가 확장 된 마이크로 아키텍처도 새로운 CPU 코어를 가지고 있다. 하지만 미드 레인지는 명령어 세트도 마이크로 아키텍처도 오래된 Cortex-A9 상태였다. ARM은 ARMv7 확장 아키텍처에서 더욱 발전된 마이크로 아키텍처의 중급 CPU를 필요로 했다. 그 대답이 Cortex-A12 셈이다.

무엇보다, ARM의 로드맵은 여전히 빠져있다. Cortex-A12 조금 전에 등장하는 프리미엄 CPU의 Cortex-A57와 엔트리 레벨 CPU의 Cortex-A53는 64 bit 명령을 포함 ARMv8 아키텍처이더라도, 그것은 최신 Cortex-A12가 32-bit의 ARMv7 아키텍처 기반이다. 따라서 현재는 중급에만 ARMv8 64-bit 아키텍처의 CPU 코어가 빠져있다.

여기에는 두 가지 이유가있다. 첫째, Cortex-A53는 엔트리 레벨 CPU하지만, 그 이상으로 Cortex-A57와 big.LITTLE에서 결합 CPU 코어 인 것이다.따라서 프리미엄 Cortex-A57 때 A53도 필요하다. 반면 중급 CPU는 big.LITTLE에서 프리미엄 CPU와 결합 필연성이 없기 때문에 ARMv8에 가지런히 할 필요가 없다.

다른 하나는 이미 설명했듯이 Cortex-A15와 동 세대의 코어가 중급이 결여되는 것이다. 따라서 ARM 먼저 ARMv7 확장 버전의 CPU를 내고 다음 64-bit ARMv8 버전을 낼 것으로 보인다. ARM은 모바일에서는 64-bit는 하이 엔드부터 단계적으로 침투하는 것으로 생각하고 있으며,이를 위해 미드 레인지를 뒷전으로 했다고 추측된다. 그러나 소프트웨어 업체 측은 코드베이스를 가능한 균질화하려는 것이고, ARM의 의도에서 벗어난지도 모른다.

NEON SIMD 엔진 등을 완벽하게 통합

또한 Cortex-A12는 기존의 기본 용도는 틀에서도 벗어났다. Cortex-A9는 여전히 옵션으로 취급했다 FPU / NEON SIMD (Single Instruction, Multiple Data) 엔진의 파이프 라인이 완벽하게 통합되었다. "Cortex-A12와 Cortex-A9의 가장 큰 차이점 중 하나는 종래는 옵션이었다 NEON SIMD/VFPv4 FPU가 통합 된 것이다. 또한 L2 캐시 관리도 완벽하게 통합됐다"고 ARM의 Brochier 씨는 설명한다.

ARM이 NEON 등을 분리 한 옵션 단위로 한 것은 Cortex-A9가 임베디드 시장에서 사용될 가능성을 의식한 것이었다. 또한 Cortex-A9을 개발하고 2007 년경 상황에서는 부동 소수점 / SIMD 연산 성능을 모바일도 중요하게 되는 것을 상정하고 있었다. ARM의 Bruce 씨는 다음과 같이 말한다.

"정직하게 말하면, 6 년 전 스마트폰에서 부동 소수점 연산 성능은 그렇게 중시하지 않았다. 또한, 내장에 사용되는 경우도 상정하고, NEON을 개별 유닛했다. 그러나 상황은 바뀌고 현재는 이미 부동 소수점 연산 유닛과 NEON은 표준 형상이 되었다고 생각한다. 그 이유 중 하나는 소프트웨어 기반이 완전히 바뀌어, 많은 소프트웨어가 NEON 코드를 사용하게 된 것이다. "

소프트웨어 측의 상황 변화가 CPU 마이크로 아키텍처의 변화도 촉구했다.

원본 글 : http://pc.watch.impress.co.jp/docs/column/kaigai/20131111_622938.html

'Hardware' 카테고리의 다른 글

| AMD가 차기 APU "Kaveri"의 개요를 발표 (0) | 2013.11.14 |

|---|---|

| Apple, Thunderbolt2 탑재의 MacBook Pro 및 Mac Pro (0) | 2013.10.23 |

| Intel, Arduino 호환 마이크로 컨트롤러 개발 보드 "Galileo" (0) | 2013.10.04 |